34 измененных файлов с 9 добавлено и 1 удалено

+ 1

- 0

bsp/wch/risc-v/Libraries/Kconfig

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/.config → bsp/wch/risc-v/ch32v208w-r0/.config

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/Kconfig → bsp/wch/risc-v/ch32v208w-r0/Kconfig

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/SConscript → bsp/wch/risc-v/ch32v208w-r0/SConscript

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/SConstruct → bsp/wch/risc-v/ch32v208w-r0/SConstruct

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/applications/SConscript → bsp/wch/risc-v/ch32v208w-r0/applications/SConscript

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/applications/main.c → bsp/wch/risc-v/ch32v208w-r0/applications/main.c

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/board/Kconfig → bsp/wch/risc-v/ch32v208w-r0/board/Kconfig

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/board/SConscript → bsp/wch/risc-v/ch32v208w-r0/board/SConscript

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/board/board.c → bsp/wch/risc-v/ch32v208w-r0/board/board.c

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/board/board.h → bsp/wch/risc-v/ch32v208w-r0/board/board.h

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/board/linker_scripts/link.lds → bsp/wch/risc-v/ch32v208w-r0/board/linker_scripts/link.lds

+ 0

- 0

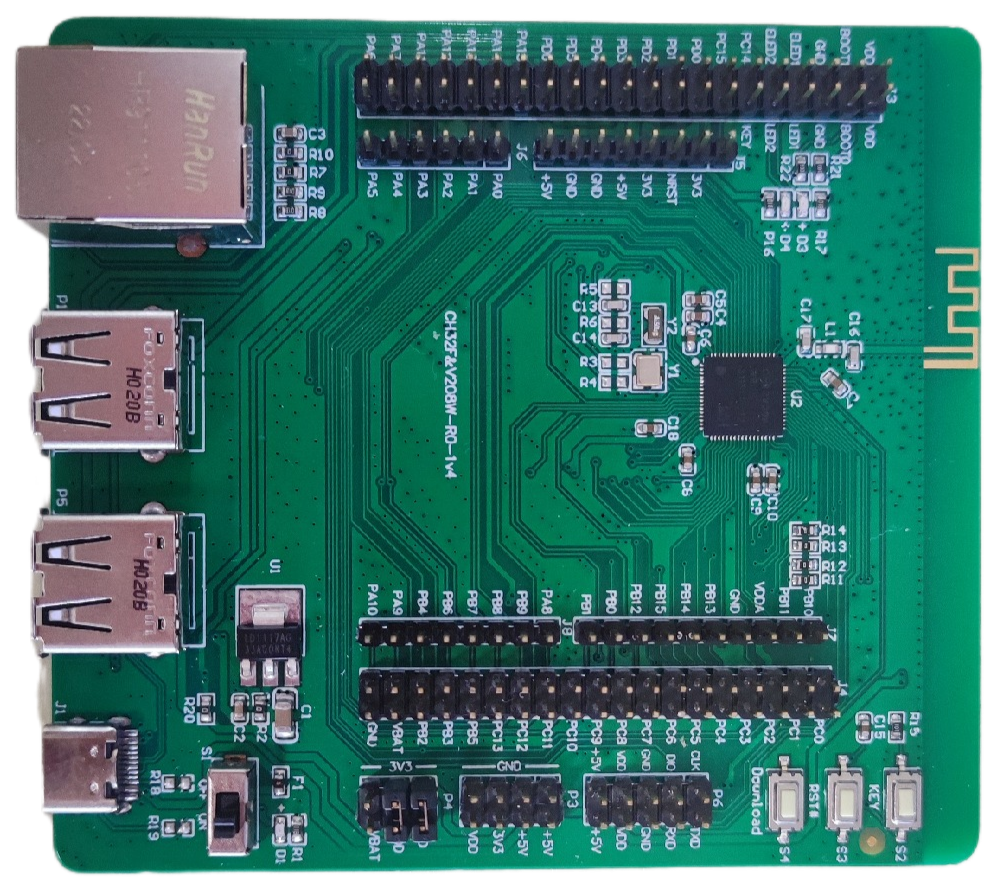

bsp/wch/risc-v/ch32v208v-r0/figures/ch32v208.png → bsp/wch/risc-v/ch32v208w-r0/figures/ch32v208.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/config.png → bsp/wch/risc-v/ch32v208w-r0/figures/config.png

+ 0

- 0

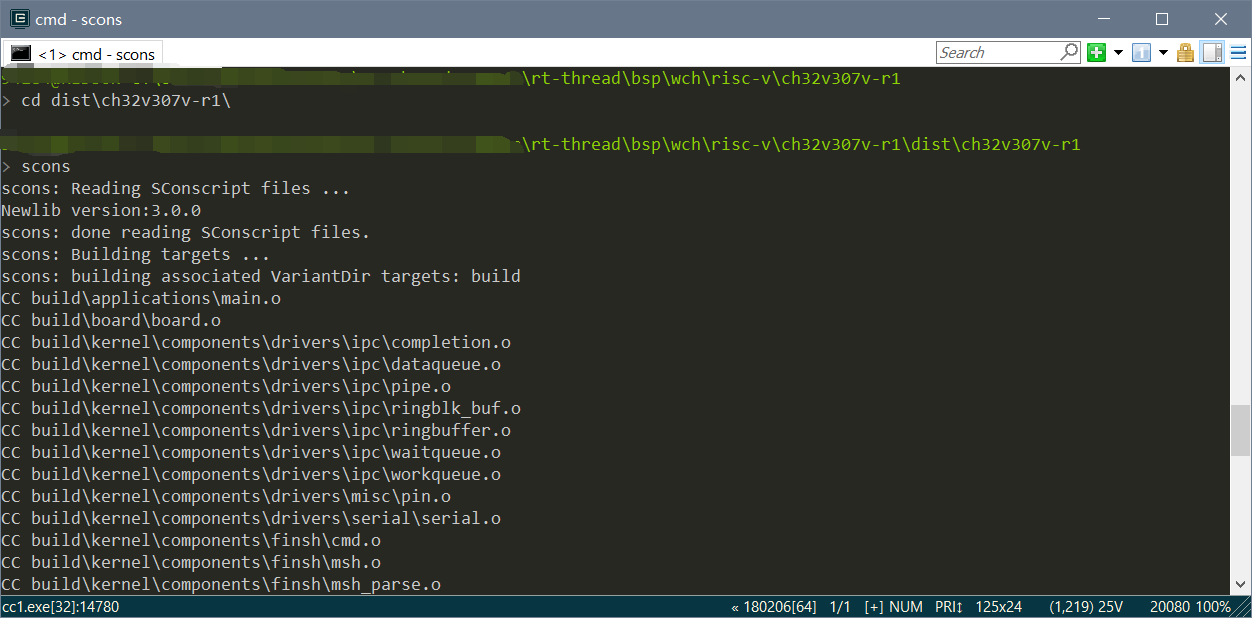

bsp/wch/risc-v/ch32v208v-r0/figures/dist.png → bsp/wch/risc-v/ch32v208w-r0/figures/dist.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/end.png → bsp/wch/risc-v/ch32v208w-r0/figures/end.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/import.png → bsp/wch/risc-v/ch32v208w-r0/figures/import.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/prefix.png → bsp/wch/risc-v/ch32v208w-r0/figures/prefix.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/scons.png → bsp/wch/risc-v/ch32v208w-r0/figures/scons.png

+ 0

- 0

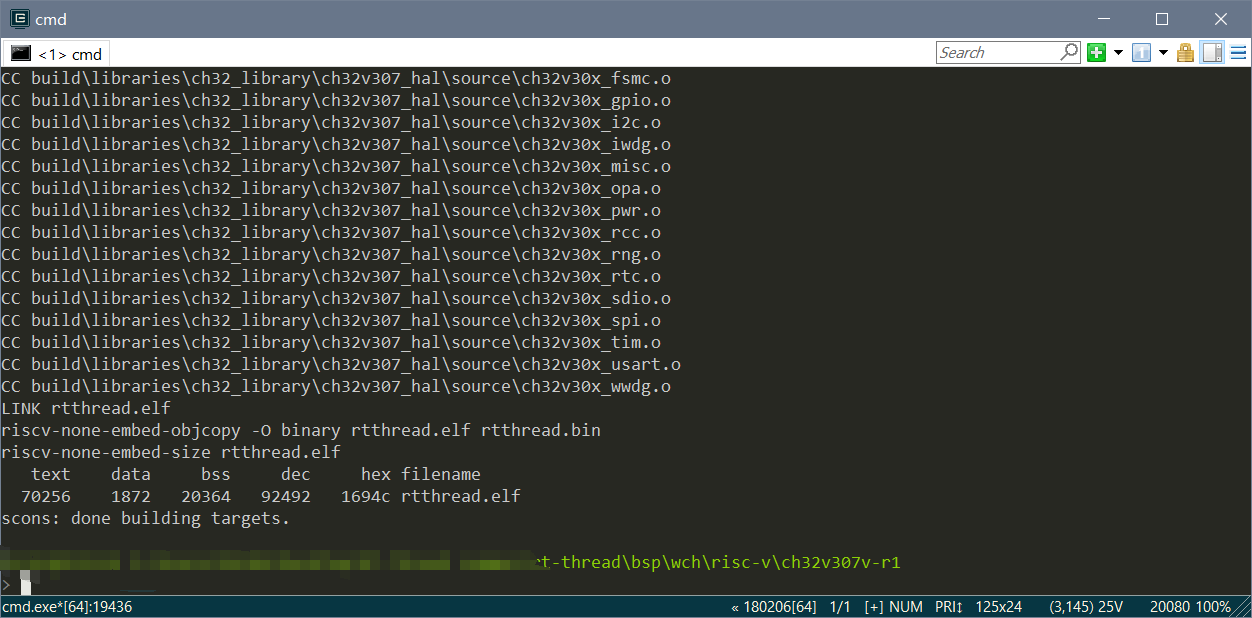

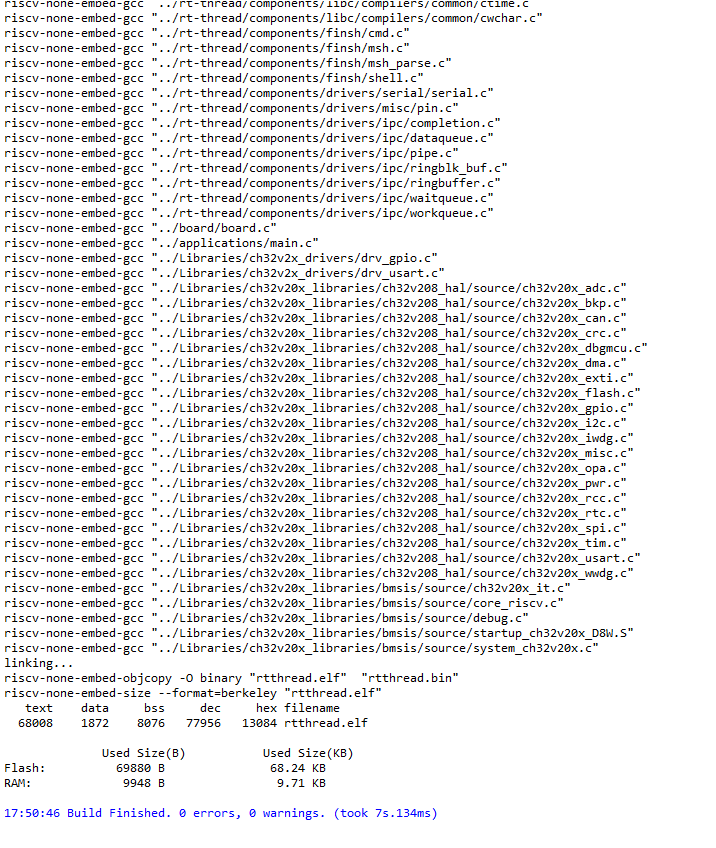

bsp/wch/risc-v/ch32v208v-r0/figures/sconscompile.jpg → bsp/wch/risc-v/ch32v208w-r0/figures/sconscompile.jpg

+ 0

- 0

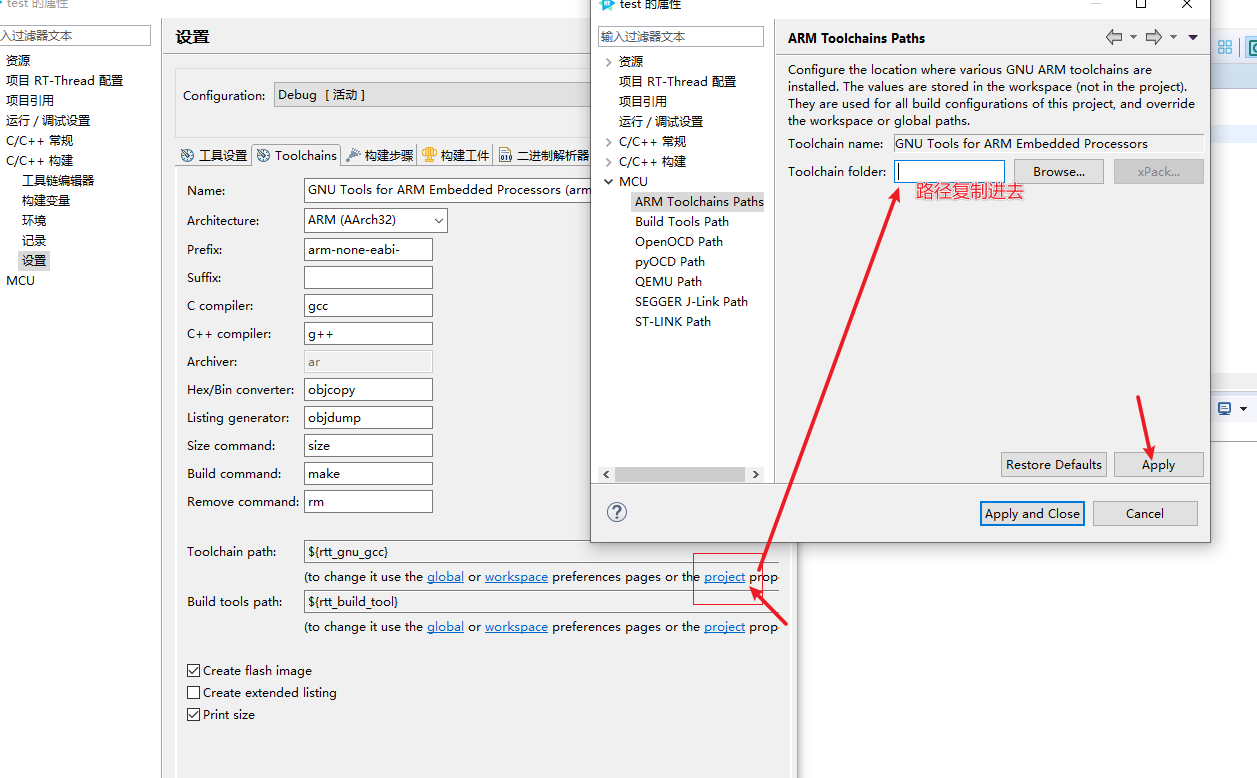

bsp/wch/risc-v/ch32v208v-r0/figures/set.png → bsp/wch/risc-v/ch32v208w-r0/figures/set.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/success.png → bsp/wch/risc-v/ch32v208w-r0/figures/success.png

+ 0

- 0

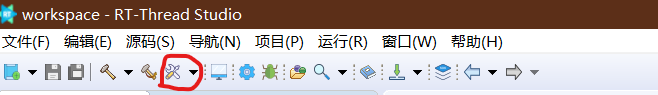

bsp/wch/risc-v/ch32v208v-r0/figures/tool.png → bsp/wch/risc-v/ch32v208w-r0/figures/tool.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/toolchain.png → bsp/wch/risc-v/ch32v208w-r0/figures/toolchain.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/toolset.png → bsp/wch/risc-v/ch32v208w-r0/figures/toolset.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/vscode-terminal.png → bsp/wch/risc-v/ch32v208w-r0/figures/vscode-terminal.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/figures/windows.png → bsp/wch/risc-v/ch32v208w-r0/figures/windows.png

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/README_zh.md → bsp/wch/risc-v/ch32v208w-r0/readme.md

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/rtconfig.h → bsp/wch/risc-v/ch32v208w-r0/rtconfig.h

+ 0

- 0

bsp/wch/risc-v/ch32v208v-r0/rtconfig.py → bsp/wch/risc-v/ch32v208w-r0/rtconfig.py

+ 1

- 0

libcpu/risc-v/ch32/context_gcc.S

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

+ 1

- 0

libcpu/risc-v/ch32/cpuport.c

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

+ 1

- 0

libcpu/risc-v/ch32/interrupt_gcc.S

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

+ 5

- 1

libcpu/risc-v/common/context_gcc.S

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||